实现容错量子计算是量子计算技术发展的终极目标,其先决条件是量子门的错误率低于容错阈值,然后利用大量冗余比特进行纠错。在保持量子相干性的条件限制下,进行纠错需要的大量冗余比特计算资源是当前实现容错量子计算的主要障碍。理论研究表明,降低门操作错误率可以有效降低所需计算资源,因此提高门操作性能是实现量子容错量子计算的首要任务。

超导量子计算是目前最有可能实现实用量子计算机的候选方案之一,在当前的超导量子处理器架构中,由超导量子比特高能级之间的耦合引起的寄生ZZ耦合是限制量子门操作和量子纠错性能的一个主要因素,近日,于扬课题组提出了一种可以实现高对比度ZZ耦合的全新超导量子处理器架构,基于此处理器架构,我们不仅可以用高开/关比来控制ZZ耦合,以实现高保真度两比特CZ门,而且也可以抑制ZZ耦合,实现高保真度两比特iSWAP门,此外,还可以抑制近邻比特间的ZZ串扰。因此,该方法对于实现容错的超导量子计算具有重要意义。

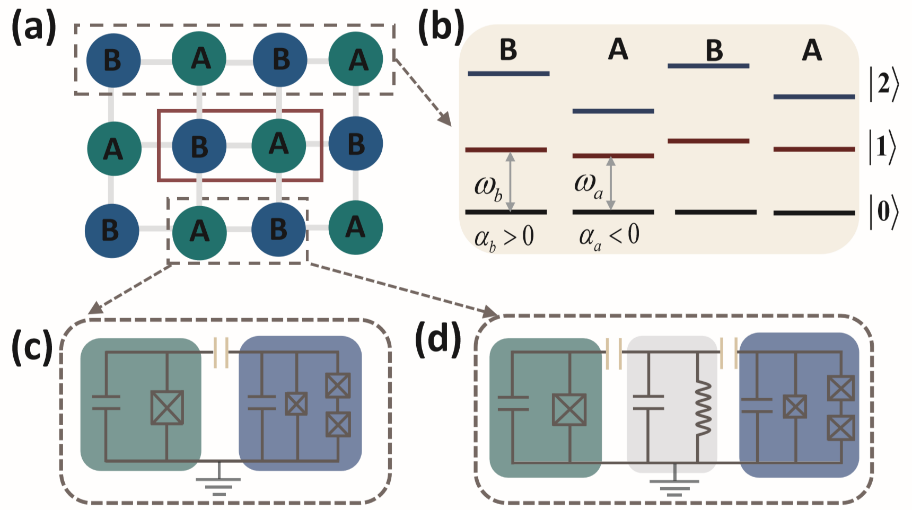

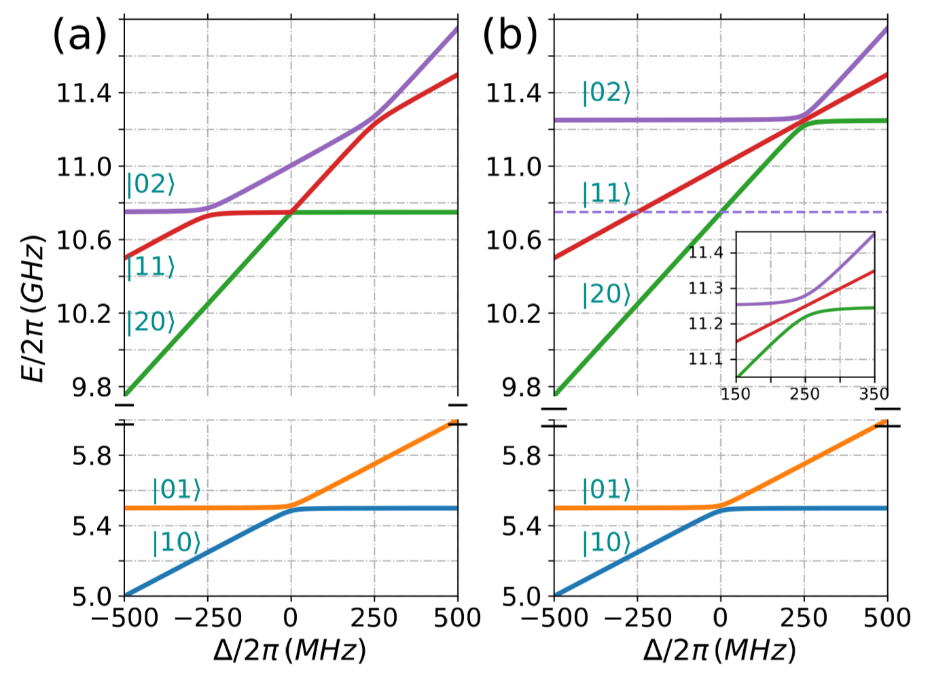

图1为于扬课题组提出的超导量子处理器架构,其中,具有相反非谐性的A类型量子比特和B类型量子比特交错排列,通过近邻耦合形成二维点阵结构。课题组选用非谐性为负的Transmon量子比特作为A类型量子比特,非谐性为正的C-shunt flux量子比特作为B类型量子比特,并通过电容耦合或谐振腔耦合来实现近邻耦合。相比于当前普遍使用的由单一种类超导量子比特构成的处理器架构,二者的能级结构具有显著的差别,如图2所示。其中图2(a)表示由两个非谐性为负的Transmon量子比特构成的耦合体系的能级结构,图2(b)表示由非谐性恰好相反的Transmon量子比特和C-shunt flux量子比特构成的耦合体系的能级结构,后者具有一个明显的三重简并点。量子比特可以通过电容器直接耦合图1(c),或者使用谐振器进行间接耦合图1(d)。

图1 新型超导量子处理器架构

图2 两比特耦合体系的能级结构

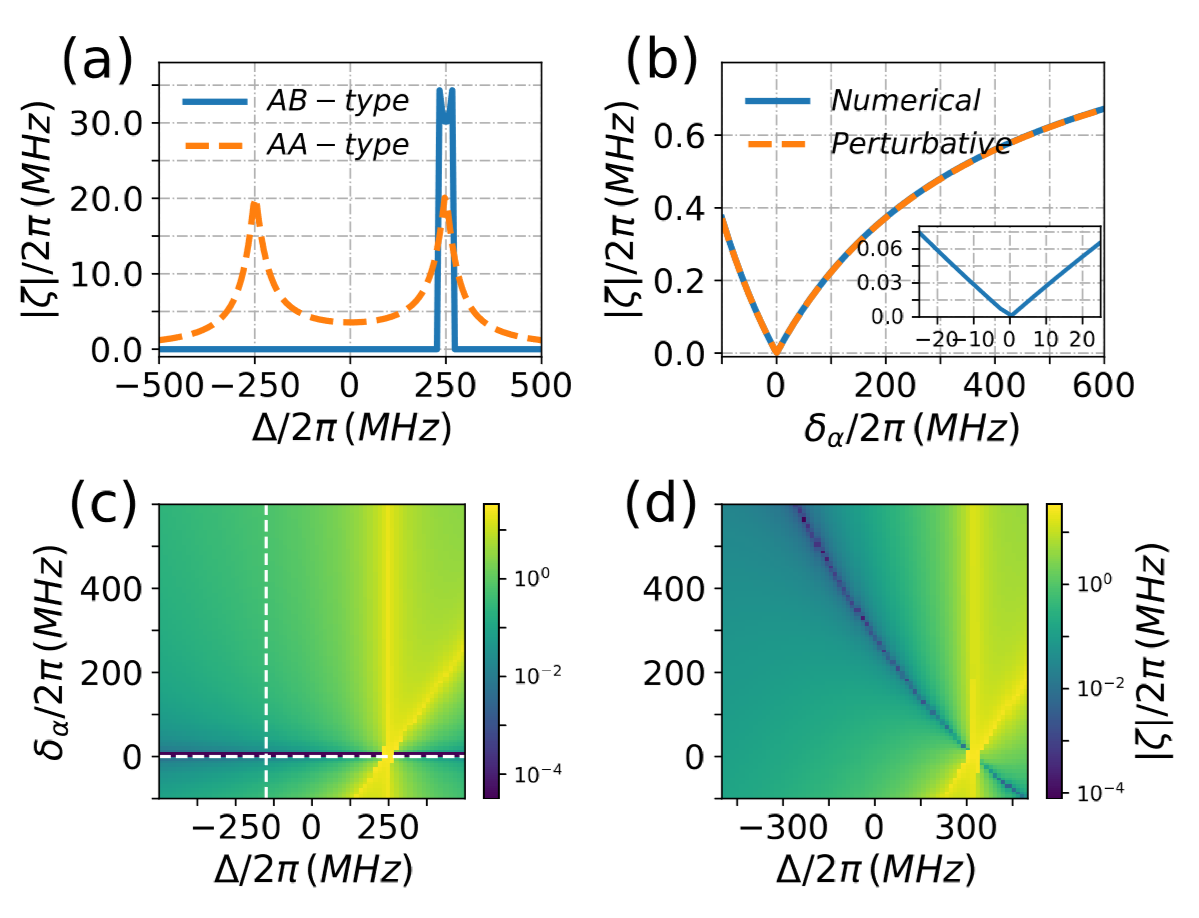

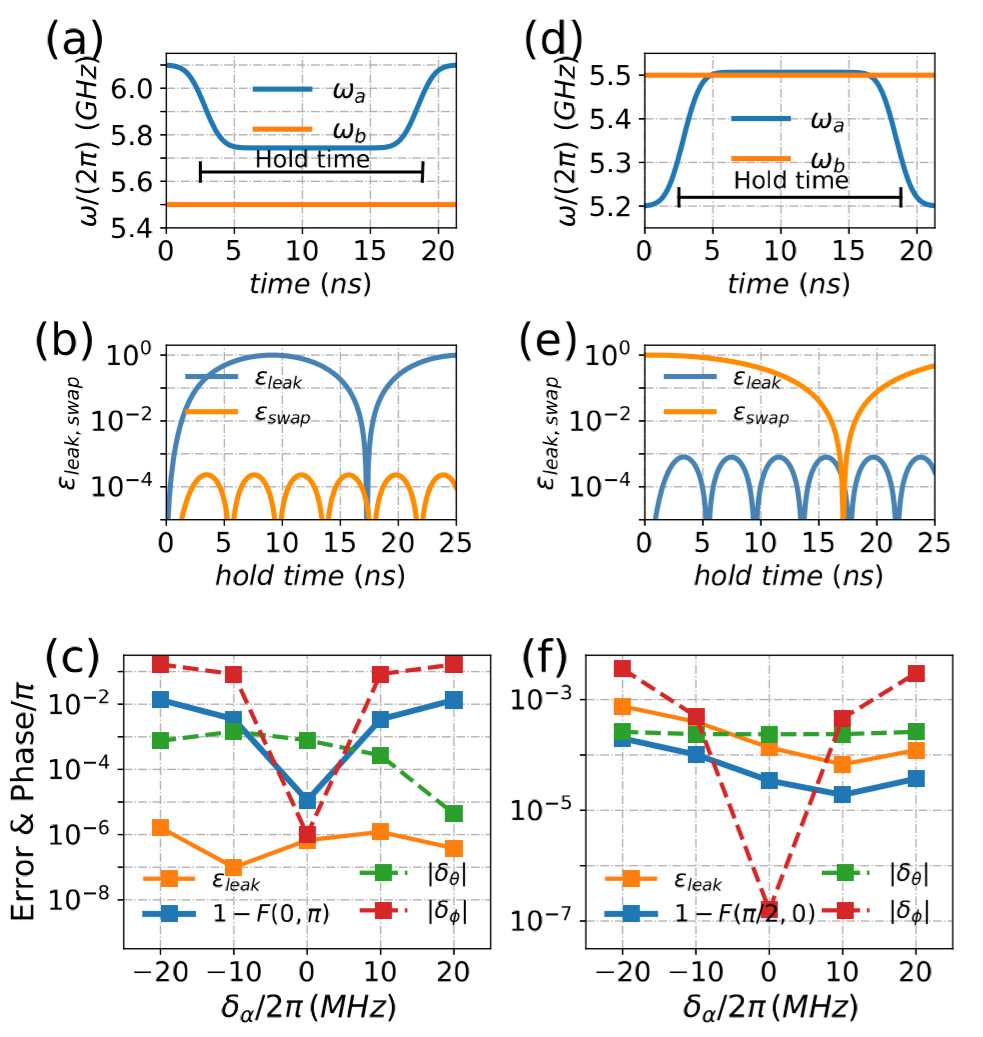

为证明提出的这类新型超导量子处理器架构的优势,课题组通过数值计算得到了ZZ耦合强度随近邻比特的失谐量及非谐性之差的变化,如图3所示,计算结果表明,该新型处理器架构确实能够实现高对比度和高开关比的ZZ耦合。此外,课题组通过计算进一步证明了,在该架构中,采用非绝热方案可以实现更快的CZ门操作和极低相位误差的iSWAP门操作,如图4所示,根据数值结果,我们可以基于此架构,实现泄露小于的iSWAP门和交换误差小于的CZ门,把目前国际上最好的两比特逻辑门保真度从2个9提高到3个9,可以大幅度地减少冗余比特的数量,对实现容错量子计算具有重要意义。

图3 ZZ耦合强度随失谐量及非谐性的变化

图4 CZ门和iSWAP门的数值计算结果

该成果于2020年11月12日在物理学顶级期刊《Physical Review Letters》上在线发表。该项课题的研究得到国家重点研发计划、国家自然科学基金委员会、江苏省自然科学青年基金及广东省重点领域研发计划支持。