在异质衬底上外延生长晶硅薄膜层是高性能空间电子、面向移动通讯和微波电子器件的关键核心技术。同时,基于绝缘衬底上的高品质晶硅薄层(即silicon-on-insulator, SOI结构)可以大幅降低高速电子器件中电路与衬底之间的寄生电容,从而获得更高的操作速度和更低的功耗。另外,使用绝缘的衬底还能直接省略传统CMOS器件中的隔离区,从而大大提高器件的集成度。基于以上考虑,在R-plane蓝宝石衬底上生长晶硅外延层(即silicon-on-sapphire,SoS)技术,一直以来,在各种极端高性能条件下的电子器件以及高功率通讯领域具有非常重要的应用。然而,传统的SoS制备工艺需要高温(>900 oC)的CVD淀积和退火再晶化工艺。由于晶硅和蓝宝石衬底之间具有较大的热膨胀系数适配(晶硅的仅为蓝宝石的二分之一),高温制备工艺后的冷却过程中会引入大量的晶格缺陷,从而严重地限制了SoS的大规模可靠制备。由于大多数SoS电子器件,以及基于SoS制备的近-中红外光波导等,最终需要的仅仅是准一维硅纳米沟道结构,所以从工艺流程的角度看,也需要研发一种“一步到位”的纳米线沟道直写技术,从而规避受应力和晶格适配限制制约的传统“平面-刻蚀-纳米沟道”SoS技术工艺挑战。

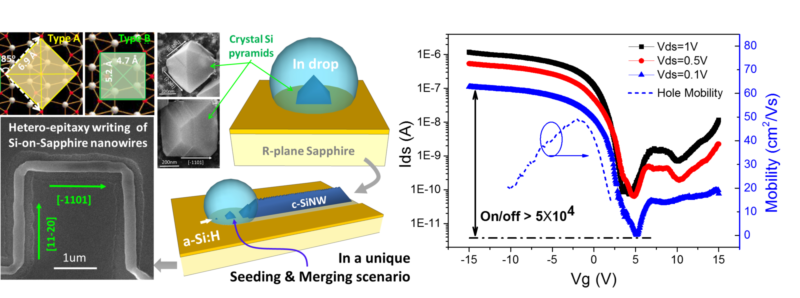

为了寻求新的突破思路解决以上限制SoS器件应用的关键问题,37000cm威尼斯电子科学与工程学院余林蔚教授、徐骏教授课题组,首次提出并展示了一种在R-plane蓝宝石衬底上直接低温异质外延生长自定向排列的晶硅纳米线技术。利用实验室自主创新的平面纳米线生长手段,仅需要在350 oC左右的工艺温度条件下,就可以在蓝宝石衬底上实现晶硅纳米线的定向生长。还进一步研究了其中本征的晶格适配对纳米线生长方向,应力和晶格质量的影响,首次揭示了其中十分新颖的“底面成核-侧向融合”生长模式,并提出了一套较为完善的平面纳米线异质外延生长的动力学模型。最后,基于绝缘衬底上的异质外延纳米线沟道制备并验证了其在高迁移率SoS-FET器件。值得一提的是,此项异质外延晶硅纳米线沟道的技术突破不仅大大降低了SoS制备中的温度和工艺复杂程度,更预示着一种金属液滴辅助下可控自组织SoS纳米线直写技术的全新思路和方案。这为发展未来高性能、极端性能大规模通讯电子器件奠定了一个核心技术基础。

本项研究成果论文,Heteroepitaxial Writing of Silicon-on-Sapphire Nanowires(异质外延SoS直写纳米线)发表在Nano Letters (纳米快报)DOI: 10.1021/acs.nanolett.6b02004之上。论文的第一作者为博士生许明坤同学,通讯作者是37000cm威尼斯余林蔚教授和徐骏教授。相关工作得到了电子科学与工程学院的施毅教授、陈坤基教授以及法国巴黎综合理工/CNRS,LPICM实验室Pere Roca i Cabarrocas教授的大力支持。该项研究工作受到“青年”,国家基础研究“973”课题,国家自然科学基金,江苏杰出青年基金,江苏省自然科学基金,双创人才计划和江苏省“333”高层次人才培养工程项目的资助。

相关链接: http://pubs.acs.org/doi/abs/10.1021/acs.nanolett.6b02004

(电子科学与工程学院 科学技术处)